High-Speed Signal Design in Flex PCB: Optimizing Performance and Integrity

I. Introduction: Why High-Speed Design in Flex PCBs Is More Complex Than Rigid Boards

Flexible printed circuit boards have transitioned from simple interconnect solutions to critical signal carriers in high-speed electronic systems. This shift is driven by the rapid evolution of data-intensive applications, where mechanical flexibility must coexist with multi-gigabit signal integrity requirements. Unlike rigid PCBs, flex circuits introduce electrical variability that becomes increasingly problematic as edge rates accelerate and timing margins shrink.

Market Drivers Behind High-Speed Flex Adoption

The demand for high-speed flex PCBs is closely tied to several fast-growing industries. Fifth-generation (5G) communication equipment relies on dense, high-frequency interconnects to support data rates well above 10 Gbps. AI accelerators and edge-computing hardware require compact, low-latency signal paths to connect processors, memory, and high-speed I/O interfaces. Wearable electronics and foldable devices depend on flex circuits to enable thin, lightweight form factors, while advanced medical imaging systems use flex and rigid-flex architectures to route high-speed signals through constrained mechanical envelopes.

Across these applications, serial data rates commonly fall in the 10–25 Gbps range, with roadmap speeds extending beyond 50 Gbps. At the same time, system miniaturization drives higher interconnect density and shorter trace lengths. While shorter interconnects reduce latency, they also push designs into regimes where impedance discontinuities, dielectric losses, and phase skew become dominant performance limiters.

Why Flex PCBs Behave Differently at High Speed

The electrical behavior of a flex PCB cannot be treated as a simple extension of rigid FR-4 design practices. Mechanical deformation is a defining characteristic of flexible circuits, and bending directly alters the physical geometry that determines characteristic impedance. Changes in trace-to-reference-plane spacing during flexing can shift impedance by several ohms, enough to cause measurable reflections in high-speed channels.

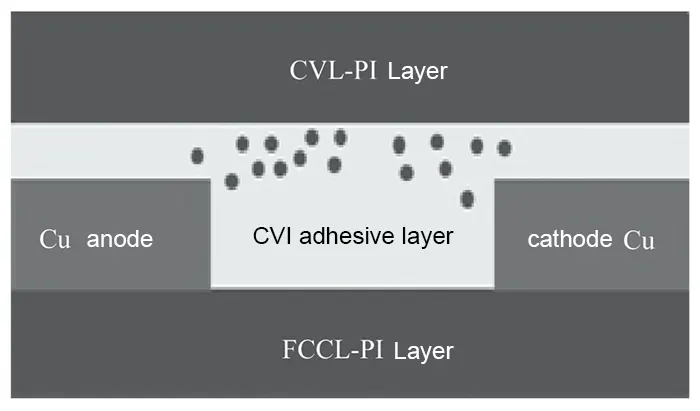

Dielectric behavior further complicates matters. Polyimide films, the dominant base material in flex PCBs, exhibit greater dielectric constant variability than rigid laminates, particularly under mechanical strain. Adhesive layers used to bond copper and dielectric films introduce additional uncertainty, as their dielectric constant (Dk) and dissipation factor (Df) are typically higher and less tightly controlled than those of the base polyimide. At multi-GHz frequencies, even small increases in Df translate into significant insertion loss.

Ground reference continuity is another challenge. Flex designs often operate with fewer layers and narrower reference planes, increasing the likelihood of return-path discontinuities. At high speed, these discontinuities manifest as increased loop inductance, mode conversion in differential pairs, and elevated electromagnetic emissions.

Scope of This Guide

This guide addresses high-speed flex PCB design from a signal integrity and manufacturability perspective. It examines the underlying physics of high-speed signal propagation, explains loss mechanisms specific to flexible substrates, and discusses practical methods for controlling crosstalk and impedance. Stack-up optimization, validation through simulation, and integration with design-for-manufacturing (DFM) processes are treated as essential elements rather than afterthoughts.

II. Fundamentals of High-Speed Signal Behavior in Flex PCB

When Is a Signal Considered "High-Speed"?

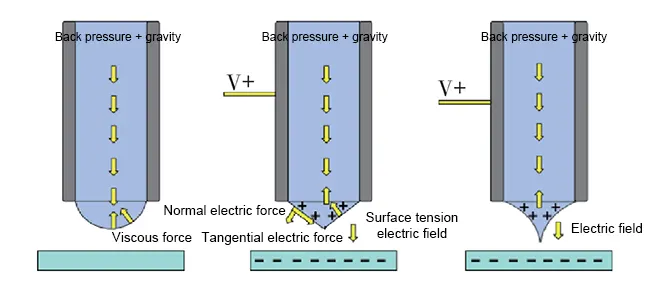

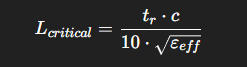

In flex PCB design, a signal becomes "high-speed" when the physical length of the interconnect is no longer negligible relative to the signal rise time. A commonly accepted engineering guideline defines the critical trace length as:

where trt_r is the signal rise time, cc is the speed of light, and εeff\varepsilon_ is the effective dielectric constant.

For example, with a 50 ps rise time and an effective dielectric constant of approximately 3.2 (typical for polyimide-based flex), the critical length is roughly 3–4 mm. Traces longer than this threshold must be treated as transmission lines, regardless of whether the overall channel length appears short by traditional standards.

Transmission Line Theory in Flexible Substrates

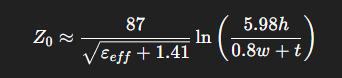

High-speed flex PCB traces operate as transmission lines whose characteristic impedance depends on conductor geometry and dielectric properties. For a microstrip structure, which is common in single-layer or surface-layer flex designs, the characteristic impedance can be approximated by:

where hh is the dielectric thickness, ww is the trace width, and tt is the copper thickness.

Flex designs typically favor microstrip geometries for manufacturability and flexibility, but striplines are sometimes used in rigid-flex regions to improve shielding and impedance stability. The table below highlights the practical trade-offs between these structures in flex environments.

| Parameter | Microstrip in Flex | Stripline in Flex / Rigid-Flex |

|---|---|---|

| Dielectric loss | Lower | Higher |

| EMI control | Moderate | Strong |

| Sensitivity to bending | High | Lower |

| Fabrication complexity | Lower | Higher |

Dielectric constant variation is particularly impactful in flex PCBs. Polyimide materials commonly exhibit Dk values between 3.1 and 3.5 at 1 GHz, with frequency dependence and strain-induced variation that can exceed ±5%, directly affecting impedance and phase delay.

Skin Effect and Frequency Dependence

At gigahertz frequencies, conductor losses are dominated by skin effect, which confines current to a thin region near the copper surface. The skin depth in copper at 10 GHz is approximately 0.65 µm, meaning that surface quality plays a critical role in loss performance.

Electrodeposited (ED) copper, while common in rigid boards, has relatively high surface roughness, which increases effective resistance at high frequencies. Rolled annealed (RA) copper offers a smoother surface and superior grain structure, resulting in lower insertion loss and better mechanical endurance under repeated bending.

| Copper Type | Typical RMS Roughness | High-Frequency Loss Trend |

|---|---|---|

| ED Copper | 4–6 µm | Higher |

| RA Copper | <1 µm | Lower |

For high-speed flex applications above 10 Gbps, RA copper is generally considered the preferred choice.

III. Impedance Control in Flex PCB High-Speed Design

Target Impedance Standards

High-speed flex PCB designs typically adhere to industry-standard impedance targets. Single-ended traces are commonly designed for 50 Ω, while differential pairs target 90 Ω or 100 Ω, depending on the interface. These impedance values are widely used across high-speed serial standards such as USB, HDMI, and PCIe, regardless of specific vendor implementations.

Variables Affecting Impedance in Flex Circuits

Impedance control in flex PCBs is complicated by a larger set of variable parameters than in rigid boards. Dielectric thickness can vary during bending, altering the effective trace geometry. Polyimide dielectric constant tolerances are broader than those of high-performance rigid laminates, and adhesive layers introduce additional dielectric contributions that are often overlooked during early design stages. Variations in copper thickness, especially when plating is involved, further contribute to impedance uncertainty.

Measured data from flex PCB fabrication studies show that a ±10 µm change in dielectric thickness can result in an impedance shift of 5–8 Ω, which is sufficient to degrade eye diagrams in high-speed links.

Practical Methods for Impedance Control

Effective impedance control in flex PCB design begins with stack-up planning in collaboration with the fabricator. Material selection, adhesive systems, and copper types must be defined early and validated using field-solver simulations that account for flex-specific material properties. Special attention is required at rigid-to-flex transitions, where abrupt changes in geometry or reference planes can create significant impedance discontinuities. Connector footprints are another frequent source of mismatch and should be impedance-matched rather than treated as purely mechanical interfaces.

Ensuring Stable Impedance in Practice

Stable impedance in flex PCBs is achieved through continuous reference planes, gradual geometry transitions, and strict control of trace dimensions in bend zones. Designs that maintain impedance steps within ±10% and avoid abrupt changes across mechanical interfaces consistently demonstrate better signal integrity margins.

IV. Signal Integrity Optimization Strategies

Reflection and Return Loss Control

Reflections in high-speed flex channels are primarily caused by impedance discontinuities. Proper termination, whether at the source or load, reduces reflection amplitude. Stub lengths must be minimized, as even millimeter-scale stubs can behave as resonant structures at multi-GHz frequencies. In rigid-flex designs, back-drilling may be applied in rigid sections to remove unused via stubs, though this technique is rarely applicable in pure flex regions.

Managing Timing and Skew

Timing control is critical for differential signaling. Length matching within ±5 mil (±0.127 mm) is a common tolerance for many high-speed interfaces, but in flex regions, phase delay consistency is often more important than absolute physical length. Bends and layer transitions can introduce differential delay that must be evaluated using simulation rather than relying solely on CAD-based length rules.

Routing Best Practices in Flex High-Speed Design

High-speed traces in flex PCBs benefit from short, direct routing paths adjacent to solid reference planes. Routing across split planes or discontinuous ground structures increases return-path inductance and degrades signal integrity. Because flex designs often operate with limited layer counts, careful plane management is essential to preserve clean return paths.

Bend Radius and Signal Integrity Impact

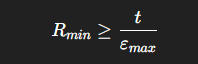

Mechanical bending imposes strain on copper traces, which can affect both reliability and electrical performance. The minimum bend radius for static flex designs is commonly estimated using:

where tt is the total flex thickness and εmax is the allowable strain, typically 0.3–0.5% for copper. From a signal integrity perspective, placing high-speed traces near the neutral axis of the flex stack-up minimizes strain-induced impedance variation. Dynamic flex applications require larger bend radii and more conservative design margins than static installations.

V. Crosstalk and EMI Control in Dense Flex Layouts

As flex PCBs move into higher data rates and denser layouts, crosstalk and electromagnetic interference (EMI) become dominant signal integrity risks. The challenge is amplified in flexible structures because conductor spacing, reference continuity, and physical geometry are not always constant across the operating lifecycle of the product.

Crosstalk Behavior in High-Speed Flex Circuits

Crosstalk in flex PCBs manifests primarily as near-end crosstalk (NEXT) and far-end crosstalk (FEXT). NEXT occurs when aggressor and victim traces share capacitive and inductive coupling near the signal source, while FEXT arises from velocity differences and mutual inductance along the coupled length. In flex designs, FEXT is often more pronounced than in rigid boards because dielectric constant variation and bending-induced spacing changes disrupt field symmetry.

At data rates above 10 Gbps, even short parallel routing segments can introduce measurable crosstalk. Simulation studies and lab measurements show that in polyimide-based flex circuits, coupled lengths as short as 5–8 mm can generate crosstalk noise exceeding 3–5% of signal amplitude, which is sufficient to reduce eye height in high-speed serial links.

Spacing Rules for High-Speed Flex PCB

Trace spacing remains one of the most effective crosstalk mitigation techniques, but spacing rules must be applied more conservatively in flex designs. The widely used 3W rule, which recommends spacing adjacent traces at least three times the trace width, typically limits near-end crosstalk to approximately –30 dB under ideal conditions. However, in dense flex layouts with variable dielectric thickness and mechanical deformation, this margin may be insufficient.

For critical high-speed nets or long parallel routing segments, designers often adopt a 5W spacing rule, which can reduce coupling by an additional 8–10 dB. In practice, high-speed signal groups are also isolated from lower-speed or noisy nets by dedicated spacing corridors or ground shielding structures, particularly in multilayer flex or rigid-flex designs.

Grounding Strategies in Flexible Areas

Ground reference quality plays a decisive role in both crosstalk suppression and EMI control. Solid ground planes provide the lowest impedance return path and the most predictable electromagnetic behavior, but they reduce flexibility and increase stiffness. Hatched ground planes are sometimes used in flex regions to improve bendability, though this comes at the cost of higher return-path inductance and increased EMI risk at high frequencies.

In multilayer flex constructions, dedicated shield layers adjacent to high-speed signal layers significantly reduce both crosstalk and radiated emissions. In rigid-flex designs, stitching vias are commonly employed in rigid sections to maintain low-impedance ground continuity between layers, even though vias are generally avoided in dynamic flex areas due to reliability concerns.

EMI Risk in Folded and Bent Structures

Folded flex structures introduce unique EMI challenges because bending can unintentionally increase loop area and distort current return paths. As loop area grows, radiated emissions increase proportionally, particularly at harmonic frequencies. Maintaining current return path integrity during folding is therefore essential.

Effective EMI control strategies include minimizing signal-reference separation, reinforcing shielding in fold regions, and ensuring that high-speed return currents always have a continuous and closely coupled ground path. In high-risk designs, additional shielding layers or conductive covers are introduced in rigid sections to compensate for unavoidable discontinuities in flex regions.

VI. Signal Loss and High-Frequency Attenuation

Insertion loss is a primary performance limiter in high-speed flex PCB channels, especially as frequencies extend into the multi-gigahertz range. Unlike rigid boards, flex circuits often rely on thinner dielectrics and adhesive systems that exacerbate both dielectric and conductor losses.

Sources of Insertion Loss in Flex PCBs

Insertion loss in flex interconnects arises from multiple contributors. Dielectric loss is governed by the dissipation factor (Df) of the substrate and adhesive materials. Conductor loss is dominated by skin effect and copper surface roughness at high frequency. Additional losses are introduced by vias, connector transitions, and rigid-to-flex interfaces, each of which can contribute measurable discontinuities.

At frequencies above 10 GHz, dielectric loss often becomes the dominant factor in polyimide-based flex circuits, particularly when adhesive layers with higher Df values are present.

Material Comparison for Low-Loss Flex Design

Material selection has a first-order impact on signal attenuation. Standard FR-4 materials, with dissipation factors typically ranging from 0.015 to 0.020 at 10 GHz, are unsuitable for high-speed flex applications. Polyimide films used in flex PCBs offer lower Df values, but these still vary depending on formulation and adhesive usage.

| Material System | Typical Df @ 10 GHz | Relative Loss Impact |

|---|---|---|

| Standard FR-4 | 0.015–0.020 | High |

| Adhesive-based polyimide | 0.008–0.012 | Moderate |

| Low-loss polyimide (adhesiveless) | 0.003–0.005 | Low |

At 10 GHz and above, reducing Df below 0.005 can lower dielectric insertion loss by more than 30–40% over typical flex stack-ups, significantly extending channel reach or improving eye margins.

Reducing Conductor Loss in Flex Circuits

Conductor loss reduction in flex PCBs begins with copper selection. Rolled annealed (RA) copper is preferred due to its smoother surface profile and superior mechanical properties. Controlling copper roughness is particularly important because surface irregularities increase effective resistance as current is confined to the outer microns of the conductor at high frequency.

Excessive copper plating thickness, while sometimes used to improve reliability, can increase surface roughness and negate high-frequency performance gains. Optimized designs balance mechanical durability with electrical loss control.

Via Optimization Techniques

Although vias are less common in pure flex regions, they remain unavoidable in rigid-flex designs. Each via introduces parasitic inductance and capacitance that contribute to insertion loss and reflection. Minimizing via count in high-speed paths is therefore critical. Where layer transitions are necessary, blind or buried vias reduce stub length and improve signal integrity. In rigid sections, back-drilling is an effective method for removing unused via stubs, reducing resonances that can severely degrade high-frequency performance.

VII. Stack-Up Engineering for High-Speed Flex PCB

Stack-up design is one of the most influential factors in achieving stable electrical and mechanical performance in high-speed flex PCBs. Poor stack-up decisions can undermine even well-routed designs.

Layer Configuration Strategy

High-speed flex and rigid-flex designs typically use 4–8 layers, depending on signal density and shielding requirements. Best practice places high-speed signal layers directly adjacent to continuous ground planes to minimize loop inductance and control impedance. This configuration also reduces susceptibility to external noise and limits EMI.

Symmetrical Stack-Up and Warpage Control

Mechanical symmetry is essential in flex PCB stack-ups to prevent warpage and uneven stress distribution. Asymmetric copper distribution or dielectric thickness can cause bending or twisting during thermal cycling, which in turn alters impedance and degrades reliability. Balanced copper weights and symmetrical layer arrangements help maintain both mechanical stability and consistent electrical performance.

Adhesive vs. Adhesive-Less Construction

Adhesive-less flex constructions eliminate the dielectric contribution of bonding layers, resulting in lower loss and more stable impedance. Electrically, adhesive-less designs offer superior high-frequency performance due to reduced Df and tighter material control. From a reliability perspective, they also perform better under thermal cycling because fewer material interfaces are present to accumulate stress.

Thermal Management in High-Speed Flex Designs

Thermal considerations are often overlooked in flex PCB design, yet temperature directly affects dielectric properties. As temperature rises, both Dk and Df increase, leading to higher loss and impedance drift. Heat tends to concentrate in rigid sections where components are mounted, making thermal vias and copper balancing essential. Effective thermal management stabilizes electrical performance and extends product lifespan.

VIII. Mechanical-Electrical Co-Design: The Hidden Factor Competitors Miss

One of the most underestimated aspects of high-speed flex PCB design is the interaction between mechanical stress and electrical performance. Designs that ignore this coupling often pass initial tests but fail under real-world operating conditions.

Neutral Axis Design for Dynamic Flex

In a bent flex circuit, the neutral axis is the plane where tensile and compressive stresses cancel. Placing high-speed traces near this axis minimizes strain during bending, reducing both mechanical fatigue and impedance variation. In multilayer flex stack-ups, careful layer ordering is required to position critical signal layers as close as possible to the neutral axis.

Reliability Under Repeated Bending

Dynamic flex applications are subject to repeated bending cycles, making reliability a primary concern. IPC standards such as IPC-2223 define flex cycle testing requirements, with some applications demanding tens of thousands of cycles. Crack prevention strategies include using RA copper, avoiding sharp corners in trace routing, and maintaining adequate bend radii.

Signal Stability During Mechanical Deformation

Mechanical deformation does not only threaten reliability; it also affects signal integrity. Measurements on bent flex circuits show impedance shifts of 5–10% in poorly optimized designs, enough to cause reflection-induced jitter at high data rates. Advanced designs use mechanical-electrical co-simulation to model real-world deformation and predict impedance variation before fabrication.

IX. Simulation and Validation Workflow

As data rates exceed 10–25 Gbps, high-speed flex PCB design can no longer rely on rule-of-thumb layouts alone. Simulation and validation must be embedded throughout the design cycle to manage the combined electrical and mechanical uncertainties inherent in flexible structures.

Pre-Layout Planning

Effective validation begins before any routing is performed. During pre-layout planning, impedance modeling is used to define trace geometry, dielectric thickness, and reference plane placement based on actual flex materials rather than nominal library values. Polyimide dielectric constant and dissipation factor are entered using frequency-dependent models to reflect real operating conditions.

Loss budget planning is equally critical at this stage. By allocating allowable insertion loss across traces, vias, connectors, and rigid-to-flex transitions, designers can determine whether the proposed channel length is feasible. For example, in a 10 Gbps serial link, a total channel loss budget of –6 to –8 dB at the Nyquist frequency is commonly used. In flex circuits, dielectric loss alone may consume over 40% of this budget if adhesive layers are not carefully controlled.

Post-Layout Verification

Once routing is complete, post-layout verification focuses on identifying parasitic effects that cannot be predicted by geometry rules alone. Three-dimensional electromagnetic (3D EM) simulation is used to analyze impedance continuity, coupling, and radiation effects in critical regions such as bends, rigid-to-flex interfaces, and connector transitions.

Time-domain reflectometry (TDR) validation complements simulation by revealing impedance discontinuities along the signal path. In well-optimized high-speed flex designs, measured impedance variation is typically maintained within ±10% of the target value, which is generally sufficient to prevent excessive reflections at multi-gigabit data rates.

Prototype Testing

Simulation results must ultimately be confirmed through physical testing. Eye diagram measurements provide a direct view of timing margin, jitter, and noise under real operating conditions. In high-speed flex channels, eye closure is often caused by a combination of dielectric loss and impedance variation induced by bending.

S-parameter measurements, particularly insertion loss (S21) and return loss (S11), are used to validate frequency-domain performance up to the highest relevant harmonic. Environmental stress testing, including thermal cycling and controlled bending, is increasingly employed to evaluate signal stability under realistic mechanical conditions. These tests often reveal performance degradation that is not visible in static measurements, underscoring the importance of combined electrical and mechanical validation.

X. DFM Considerations for High-Speed Flex PCB

Design-for-manufacturing (DFM) plays a decisive role in the success of high-speed flex PCB projects. Even electrically sound designs can fail if they exceed fabrication capabilities or fail to account for process variability.

Manufacturing Constraints in Flex Circuits

Flex PCB fabrication imposes stricter constraints than rigid board manufacturing. Minimum trace width and spacing in flex zones are typically larger due to material handling and yield considerations. Copper thickness tolerance is also more variable, particularly in plated structures, which directly affects impedance control.

Bend areas introduce additional restrictions. Vias are generally prohibited in dynamic bend zones because they act as stress concentrators and increase the risk of cracking. Designs that ignore these constraints often suffer from reduced yield or early field failures.

Communicating Requirements to Fabricators

Clear communication with fabricators is essential to achieving predictable high-speed performance. Stack-up documentation must explicitly define material types, copper profiles, adhesive systems, and target impedance values. Rather than specifying idealized numbers, designers should state acceptable impedance tolerances, with ±10% being a common and achievable target for controlled-impedance flex designs.

Early alignment between design and fabrication teams reduces ambiguity and ensures that simulation assumptions reflect real manufacturing processes.

Avoiding Costly Redesigns

Redesigns in flex PCB projects are particularly expensive due to tooling costs and longer fabrication cycles. Early DFM reviews help identify manufacturability risks before layout is finalized. When simulation results are shared with fabricators, process adjustments can be made proactively, such as modifying dielectric thickness or copper weight to meet impedance targets without altering routing. This collaborative approach significantly reduces iteration cycles and accelerates time to production.

XI. Common High-Speed Flex PCB Design Mistakes

Despite growing awareness, several design errors continue to undermine high-speed flex PCB performance. One frequent issue is underestimating the electrical impact of adhesive layers, which often contribute disproportionately to dielectric loss at high frequency. Another common mistake is routing high-speed traces across bend lines, where mechanical strain can induce impedance variation and long-term reliability issues.

Poor reference plane continuity remains a recurring problem, especially in dense flex layouts with limited layer counts. Excessive via usage in high-speed paths introduces unnecessary discontinuities, while neglecting to specify copper roughness allows high-frequency conductor loss to exceed simulated expectations. Each of these issues can individually degrade performance; together, they often result in marginal or unstable designs.

XII. Conclusion: Engineering Flex PCB for High-Speed Reliability

High-speed flex PCB design demands a holistic engineering approach in which electrical integrity and mechanical reliability are developed in parallel. Controlled impedance, low-loss materials, and robust grounding strategies form the electrical foundation, while thoughtful stack-up design and mechanical stress management ensure long-term reliability.

Simulation and validation workflows are no longer optional. They are essential tools for managing the complexity of multi-gigabit flex interconnects and bridging the gap between design intent and manufactured reality. When combined with early DFM collaboration, these practices enable predictable performance and reduce costly redesign cycles.

As data rates continue to rise and form factors become more constrained, high-speed flex PCB expertise is no longer a niche capability. It is a competitive engineering advantage that directly influences product performance, reliability, and time to market.

References

IPC-2223, Sectional Design Standard for Flexible Printed Boards

IPC-6013, Qualification and Performance Specification for Flexible Printed Boards

Eric Bogatin, Signal and Power Integrity – Simplified

Howard Johnson & Martin Graham, High-Speed Digital Design

IEEE High-Speed Serial Interface Design Guides

Prismark, Flexible Circuit and Rigid-Flex Market Report 2024